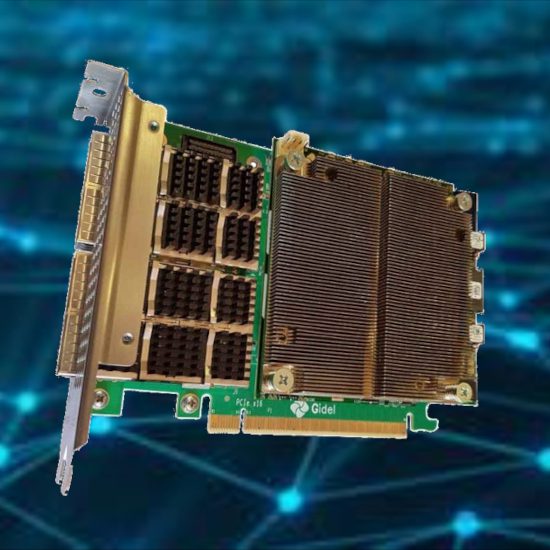

High Performance Scalable Compute Accelerators

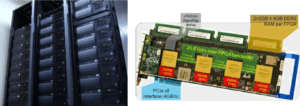

- Stratix 10 GX/SX FPGA

- Up to 2,800K logic elements

- For SX devices, Quad-core 64-bit ARM Cortex-A53 MPCore processor, contact Gidel.

- PCIe x16 Gen. 3 or stand-alone

- Up to 16× 25 Gb/s reconfigurable transceivers (total of 400 Gb/s)

- Supported by the Proc Dev Kit FPGA Programming SDK

- Form factor: full-height, double-slot, ¾ length PCI Express card

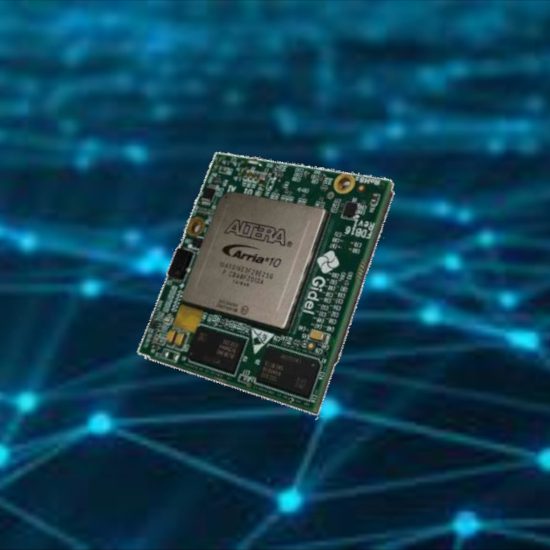

Proc10S: Accelerator Board

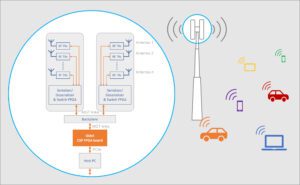

The Proc10S™ is a high-performance, scalable accelerator board built on Altera Stratix® 10 GX FPGA technology. Designed for compute-intensive, high-bandwidth, and low-latency workloads, it not only delivers peak single-precision performance of up to 10 TFLOPS but also ensures the flexibility needed for next-generation Data Centers applications. With 2.8 million logic elements, 260 GB DDR4 memory, and an optional Quad-core 64-bit ARM Cortex-A53 processor, the Proc10S provides the processing power and adaptability required for evolving infrastructures.

Performance and Memory

This powerful accelerator integrates a 16-lane PCIe Gen3 interface with 25/14.1 Gb/s SERDES transceivers for ultra-fast connectivity. Additionally, it supports up to 400 Gb/s throughput via 4 × QSFP28 or a combination of 2 × QSFP28, 2 × SFP28, and Gidel’s proprietary high-speed PHS connector. As a result, the Proc10S delivers unmatched bandwidth and responsiveness for HPC, storage, networking, and real-time data-processing environments.

Connectivity and Expansion Options

The Proc10S offers abundant I/O and expansion capabilities, ensuring seamless integration into diverse Data Centers infrastructures. Furthermore, its flexible architecture supports a wide range of applications, including broadcasting, video analytics, 5G infrastructure, and security tasks such as deep packet inspection and fraud detection. Consequently, it provides the scalability and versatility required to address the most demanding workloads.

Development Tools

Supported by Gidel’s advanced development suite, the Proc10S accelerator board streamlines integration and simplifies development. Moreover, it supports C and HDL-based workflows, reducing engineering effort, enhancing reliability, and shortening time-to-market for mission-critical solutions. In addition, its robust toolchain allows developers to maximize FPGA resources efficiently, ensuring long-term value in high-performance environments.

Why Choose the Proc10S Accelerator Board?

-

Altera Stratix® 10 FPGA with up to 2.8 million logic elements.

-

260 GB DDR4 memory with optional ARM Cortex-A53 SoC.

-

Up to 10 TFLOPS single-precision performance.

-

400 Gb/s total I/O bandwidth with PCIe Gen3 × 16 and QSFP28 ports.

-

Ideal for Data Centers, HPC, 5G, security, and AI workloads.

For more accelerator board options, refer to FPGA Compute Acceleration – Gidel

General

- Embedded MLAB (640-bit) SRAM blocks

- 11,721 M20K (20K-bit) SRAM blocks

- Up to 256 GB DDR4 SDRAM SoDIMM with throughput of up to 13.5 GB/s

- 4 GB on-board DDR4 SDRAM with throughput of up to 48 GB/s

- Up to 2,800K logic elements

- H-TILE supporting up to 16x 25 Gb/s SERDES I/O

- For SX devices, Quad-core 64 bit ARM Cortex-A53 MPCore processor

- Peak fixed-point performance 23.0 TMACS

- Peak floating-point performance 9.2 TFLOPS

- M20K blocks at up to 58 TB/s sustain access

- Up to 11,520 18x19 variable precision multipliers

- Up to 10x 25 Gb/s reconfigurable transceivers

- Quad-core 64-bit ARM Cortex-A53 MPCore @ max processor speed of 1.5 GHz

- Flexible clocking system

- Temperature monitoring

- Internal voltage monitoring

- Support for Partial Reconfiguration and CvP

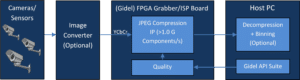

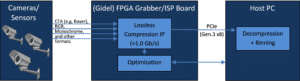

Connectivity

- 4x QSFP28

- 2x SFP28

- Gidel proprietary high-speed (PHS) connector

Environmental conditions

- Continuous Operation: 10 - 80% (non-condensing)

- Peak Operation: 10 - 90% (non-condensing)

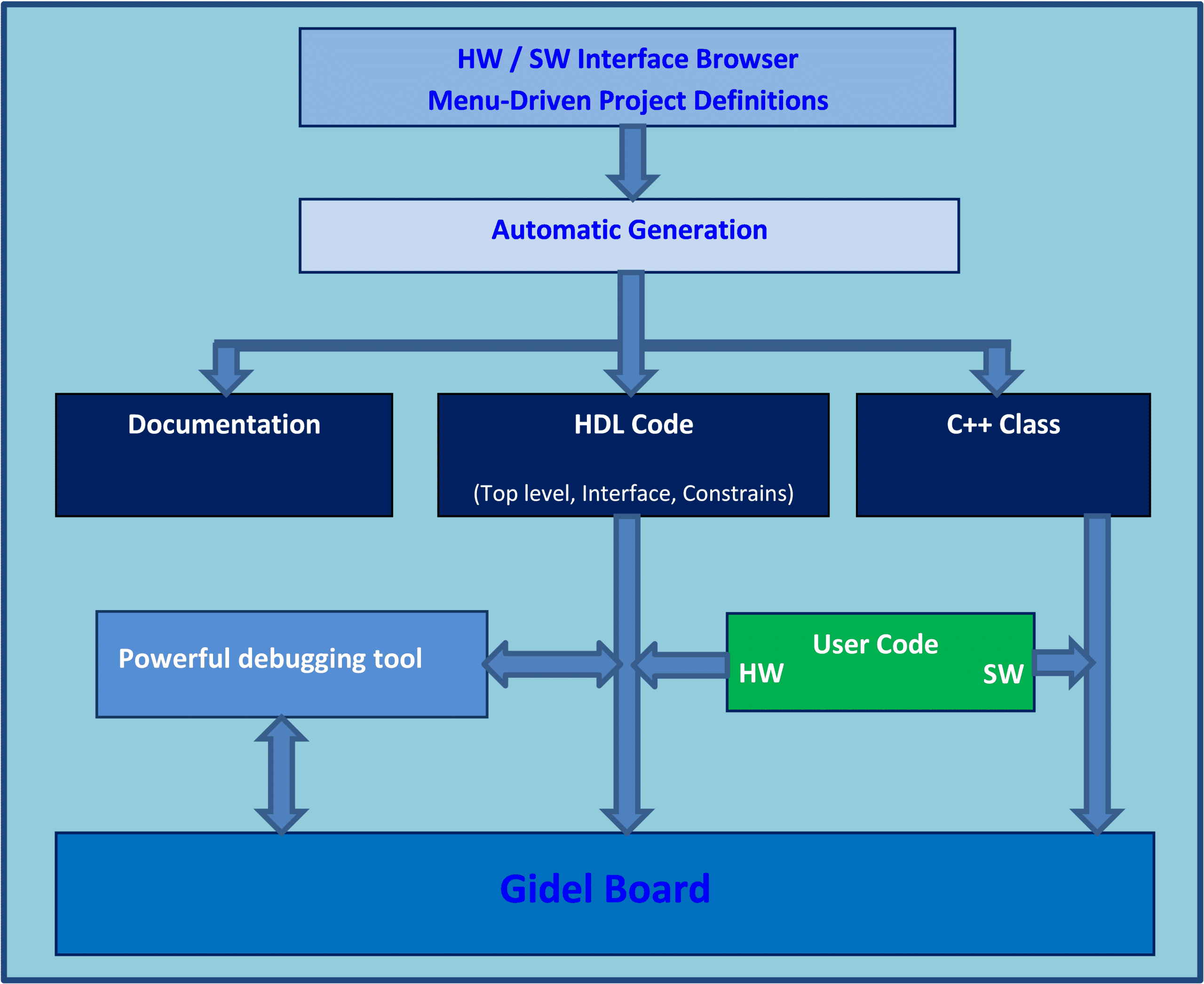

Development tools

- Generation of FPGA environment code, including all board/IP constraints and a user-logic wrapper

- Generation of a dedicated application driver with an API

- Splitting physical on-board memories into logical memories, each with independent, parallel access to/from user logic

Please contact us if you need a customized solution!

Development Tools

For HDL Design Flow

- Generation of environment FPGA code, including all board/IP constrains and user logic wrapper

- Generation of dedicated application driver with API support

- Splitting of physical on-board memories into logical memories with independent parallel access to/from user logic

- Altera Tools: Quartus Prime Pro, including QSys and DSP builder

| Name | Description | Type | Size | |

|---|---|---|---|---|

|

Proc10S

|

Datasheet | 114.7 KB | ||

|

Proc10S

|

Block Diagram | PNG | 32.0 KB |

FAQ

The Proc10S is a scalable, ultra-high-performance board built on Altera Stratix 10 GX/SX technology. It is designed for the most compute-intensive workloads in next-generation Data Centers, delivering up to 10 TFLOPS of single-precision performance. With a massive 2.8 million logic elements, it provides the density and adaptability required for evolving 5G, security, and HPC infrastructures.

The Proc10S features an extensive memory architecture to handle high-bandwidth data:

-

High Capacity: Up to 256 GB DDR4 SoDIMM with a throughput of 13.5 GB/s.

-

Low Latency: 4 GB of on-board DDR4 SDRAM with a high-speed throughput of 48 GB/s.

-

Internal Bandwidth: Embedded M20K blocks supporting up to 58 TB/s sustained access.

-

Computation: Peak fixed-point performance of 23.0 TMACS and peak floating-point performance of 9.2 TFLOPS.

The board supports an aggregate I/O bandwidth of 400 Gb/s. This is achieved through up to 16 x 25 Gb/s reconfigurable transceivers available via 4 x QSFP28 ports (or a flexible combination of QSFP28, SFP28, and Gidel’s PHS connector). For host communication, it utilizes a powerful 16-lane PCIe Gen3 interface.

Yes. For the SX device variants, the Proc10S includes a Quad-core 64-bit ARM Cortex-A53 MPCore processor running at up to 1.5 GHz. This allows for fully autonomous or tightly coupled FPGA-CPU operation, reducing the need for a separate host and enabling high-performance edge-compute and stand-alone broadcast applications.

The Proc10S is engineered for high-availability environments, featuring an MTBF exceeding 1 million hours. It supports advanced FPGA features like Partial Reconfiguration and Configuration via Protocol (CvP). Additionally, it includes integrated temperature, voltage, and clock monitoring to ensure stable operation in mission-critical Data Centers.

The Proc10S is fully supported by the Gidel ProcDev Kit (FPGA Programming SDK). The SDK streamlines development by supporting both C and HDL-based workflows, allowing developers to maximize FPGA resources efficiently while automating driver generation and system integration.

The Proc10S is the ideal engine for high-density, high-bandwidth sectors including:

-

Infrastructure: 5G Core, 5G Infrastructure, and Data Center Acceleration.

-

Security & Analytics: Deep Packet Inspection, Fraud Detection, and Network Analysis.

-

Media & Vision: Video Analytics, Broadcasting, and High-Performance Acquisition.

-

Computing: HPRC, Linear Algebra, 3D Applications, and Computational Finance.

All Gidel products come with a 12-month warranty, dedicated technical support, and regular firmware and driver updates to ensure high-performance reliability in demanding, long-term deployments.