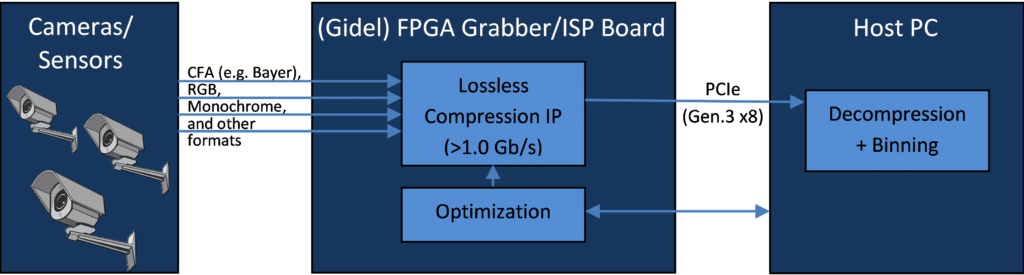

The new Gidel FPGA-based reversible compression IP reduces storage needs by over 50%, uses as little as 1% of the FPGA, and consumes under 0.2 W. This ultra-efficient design enables real-time 1 GB/sec encoding and makes the IP ideal for high-bandwidth, vision, and data-intensive applications.

Learn more about Gidel’s reversible compression IP here: Lossless Compression.

Why FPGA-Based Reversible Compression Matters Today

Renewed focus on compression and encryption IPs

Gidel announced its new real-time reversible compression IP for FPGAs, offering a breakthrough combination of speed, efficiency, and ultra-low resource usage. The solution targets the

HPC, Vision, and data-center markets—where bandwidth limits, power constraints, and storage requirements are becoming increasingly critical.

This new IP enables real-time, mathematically reversible compression—allowing the original data to be perfectly reconstructed with zero degradation. Gidel developed the IP in response to customers requiring much higher performance than commercial software compression formats can deliver. Early evaluations showed superior compression ratios, faster computation time, and dramatically lower power consumption than CPU-based alternatives.

Ultra-efficient FPGA reversible compression design (1% FPGA usage)

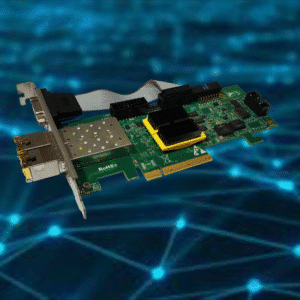

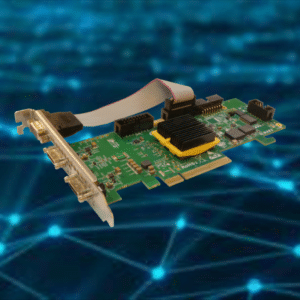

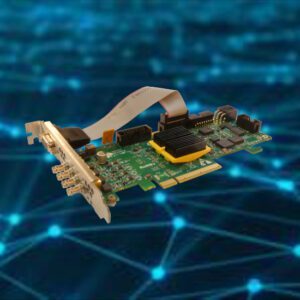

The Gidel FPGA reversible compression core uses only a small number of logic elements and consumes less than 0.2 W. For example, when running on the HawkEye Arria 10-480 board, the complete IP occupies just 1% of the FPGA silicon. This compact footprint makes it suitable for all Gidel high-performance boards—including FPGA modules and frame grabbers.

Real-time reversible compression improves system efficiency on multiple fronts. Data can be stored immediately in compressed form rather than waiting for offline processing. Memory bandwidth is also significantly improved, as less data must be transferred to host memory or SSD storage.

Boosting storage efficiency and sensor-based system performance

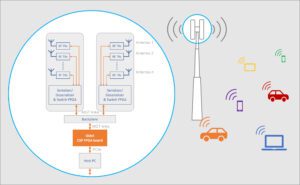

Real-time reversible compression is especially critical for systems capturing large volumes of sensor data in the field. Applications with limited storage capacity or restricted uplink bandwidth benefit immediately. By reducing data size by more than 50%, the IP effectively doubles available capacity, increases sensor count, or increases acquisition speed—depending on system requirements.

Initial tests were performed using hundreds of images supplied by Gidel’s strategic partners. The new IP is now available for customer deployments.

Part of a broader compression and encryption roadmap

Gidel offers multiple compression IPs and is preparing a family of FPGA-based encryption IPs. When deployed together—reversible compression followed by encryption—customers can build efficient and secure pipelines for cloud applications, edge systems, and imaging workflows. Both IP types are available as modular components in the Gidel tools library.

This expanded focus on compression and encryption provides strong ROI for customers by reducing power consumption and lowering storage and processing needs. Combined with Gidel’s established vision processing capabilities, the IP family is ideal for applications such as recording systems, mapping, autonomous vehicles, homeland security, and other high-bandwidth workload environments.

Gidel presented the reversible compression IP at ISC 2018 in Frankfurt, Germany (booth G-814). Visitors were able to see live demonstrations of the technology.

Related Products

-

Lossless Compression

Learn More -

FantoVision20

Learn More -

FantoVision20-CL

Learn More -

FantoVision20-GigE

Learn More -

FantoVision40

Learn More -

FantoVision40-CXP12

Learn More -

HawkEye-20GigE

Learn More -

HDR Correction

Learn More -

HawkEye-CL

Learn More -

HawkEye-CXP12

Learn More -

Proc10A-40GigE

Learn More -

Proc10A-CXP

Learn More -

Proc10M

Learn More -

Proc10N

Learn More -

Proc1C10M-120GigE

Learn More -

Proc1C10N-120GigE

Learn More -

Proc1C10N-CXP12

Learn More -

InfiniVision

Learn More -

FDB Modules

Learn More -

HawkEye

Learn More -

Proc10A

Learn More -

Proc1C10M

Learn More -

Proc1C10N

Learn More -

Proc10S

Learn More